# FPGA Design for DDR3 Memory

# Sponsored by Teradyne, North Reading, MA

A Major Qualifying Project proposal to be submitted to the faculty of Worcester Polytechnic Institute in partial fulfillment of the requirements for the Degree of Bachelor of Science

By:

Laura Fischer

Yura Pyatnychko

Submitted On: 12 March, 2012

Professor Xinming Huang, Advisor, Electrical & Computer Engineering

Professor John A. Mcneill, Advisor, Electrical & Computer Engineering

# Acknowledgements

We would like to thank:

Teradyne of North Reading, MA, including our contacts, for arranging the project and providing us with

the hardware to develop our design.

Professor Xinming Huang for his guidance and advice as an advisor throughout the project.

**Professor John A. McNeill** for organizing the project and attending to the project needs as an advisor.

# Abstract

The project presents a memory arbiter system capable of allowing two systems to communicate to the same DDR3 SDRAM memory. The arbiter was designed using Verilog, implemented using Xilinx Integrated Software Environment (ISE) and validated using iSim and ChipScope. The final design is implemented on a Virtex 6 FPGA chip. The arbiter can achieve a maximum performance of around 50 Gb/s, with the two systems reaching transfer rates of 25 Gb/s.

# **Executive Summary**

In the last 30 years, computer memory has evolved rapidly, seeing improvements in both capacity and speed. However, the logic for controlling the memory has also become increasingly more complex and difficult to interface with. The third generation of double data rate synchronous dynamic random access memory (DDR3 SDRAM) is the newest and fastest volatile memory currently available. DDR3 DRAM is one of the many types of random access memory used to temporarily hold data that the system (e.g. computer) needs to have quick access to.

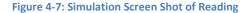

DRAM memory is designed for communication with a single system. For two systems to share the same memory, an arbiter must be used. The memory arbiter serves as an interface to both systems, and grants each system access to the memory one at a time to avoid collisions. In this project, Teradyne assigned the MQP team the task of developing a memory arbiter for DDR3 SDRAM for implementation on a Virtex 6 FPGA. The DDR3 SDRAM would be used in Teradyne's testers as data buffers between testbenches and the units under tests (UUT). The memory would enable very fast data transfer rates and significantly reduce the time the testers take to transfer data. The development of the arbiter was done on ML605 evaluation kit using Xilinx tools. Xilinx Integrated Software Environment (ISE) served as the primary work-bench for the development of the arbiter. It enabled the team to write Verilog code that describes the design of the arbiter and to insert specialized Xilinx cores, such as a DDR3 memory interface and first in first out (FIFO) blocks.

The arbiter was designed to follow a see-saw like data flow. In a two system configuration, one system is given permission to communicate with the arbiter. The permission periodically switches from one system to the other (i.e. switches alternately) regardless of whether either of systems need to send commands. When a system is given permission to the arbiter they are allowed to send read or write commands; these commands are buffered inside FIFOs within the arbiter. When system two is given permission to the arbiter, the arbiter executes the buffered commands of system one by sending them

to memory. This buffering scheme enables un-synchronized communication between the systems and the arbiter and enables heavy data throughput. Ultimately, the developed arbiter allows the systems to communicate at speeds of up to 25 Gb/s. The effective transfer rate of the two systems is dependent on both their own transfer rate and the transfer rate of the other system that is connected to the arbiter. This relationship is very similar to a model used for evaluating the equivalent resistance of two resisters connected in parallel.

Throughout the development process, the MQP team extensively tested the logic in simulation. The DDR3 SDRAM was modeled using Xilinx DDR3 memory model as well as a stimulus module developed by the team that emulated the expected behavior of the two systems. A Verilog test-bench was written for utilizing the memory model and triggering the stimulus modules. The simulation was run in Xilinx's iSim Environment. The iSim tool was very useful because its GUI easily enables the display of any signal waveform in the design. Since simulation has a fast turn-around time, the MQP team iteratively validated the design in iSim to ensure any bugs in the code were caught early. Although done less frequently, the FPGA implementation of the design was periodically validated using ChipScope. ChipScope is used to probe signals in hardware, and it provided the most accurate depiction of design behavior. However, this process required a lot more effort and was more time consuming then validating through RTL simulation.

Although the arbiter has been fully developed and is fully functional, it still needs to be properly tested with greater coverage. Functionality checkers should be developed for this design, which would test the validity of the arbiter in a run-time environment as of in practical use.

# Contents

| A  | CKNOWLEDG    | EMENTS                                       | 1  |

|----|--------------|----------------------------------------------|----|

| A  | BSTRACT      |                                              | 2  |

| E) | XECUTIVE SUI | MMARY                                        | 3  |

| т  | ABLE OF FIGU | RES                                          | 8  |

| 1. | . INTRODU    | CTION                                        | 10 |

| 2. | . BACKGRC    | DUND                                         | 12 |

|    | 2.1. RANI    | DOM ACCESS MEMORY (RAM)                      | 12 |

|    | 2.2. Stat    | IC RANDOM ACCESS MEMORY (SRAM)               | 12 |

|    | 2.3. Dyn/    | AMIC RANDOM ACCESS MEMORY (DRAM)             | 13 |

|    | 2.4. DEVE    | ELOPMENT OF DRAM                             | 14 |

|    | 2.4.1.       | DRAM                                         | 14 |

|    | 2.4.2.       | Synchronous DRAM                             | 15 |

|    | 2.4.3.       | DDR1 SDRAM                                   | 16 |

|    | 2.4.4.       | DDR2 SDRAM                                   | 16 |

|    | 2.4.5.       | DDR3 SDRAM                                   | 16 |

|    | 2.5. TIME    | LINE                                         | 17 |

| 3. | . METHOD     | OLOGY                                        | 19 |

|    | 3.1. Hari    | DWARE                                        | 19 |

|    | 3.1.1.       | Virtex-6 FPGA                                | 19 |

|    | 3.1.2.       | ML605 Board                                  | 19 |

|    | 3.2. Tool    | S                                            | 20 |

|    | 3.2.1.       | Xilinx Integrated Software Environment (ISE) | 20 |

|    | 3.2.2.       | Synthesis and Simulation                     | 22 |

|    | 3.2.3.       | Implementation and Hardware Validation       | 22 |

|    | 3.2.4.  | Analysis of Turn-Around Times        |    |

|----|---------|--------------------------------------|----|

|    | 3.2.5.  | Xilinx Core Generator                | 27 |

| 4. | IMPLEI  | MENTATION AND DESIGN                 |    |

|    | 4.1. X  | ILINX MEMORY INTERFACE GENERATOR     |    |

|    | 4.1.1.  | Memory Controller Hierarchy          |    |

|    | 4.1.2.  | Infrastructure and Clock Frequencies |    |

|    | 4.1.3.  | Validation Capabilities              |    |

|    | 4.2. IN | NTERFACING WITH THE XILINX MIG       |    |

|    | 4.2.1.  | User Interface                       |    |

|    | 4.3. A  | Arbiter Design                       | 35 |

|    | 4.3.1.  | Product Design Specifications        |    |

|    | 4.3.2.  | Design Topology                      |    |

|    | 4.3.3.  | Arbiter Flow                         | 43 |

|    | 4.3.4.  | Determining Arbiter's Performance    |    |

| 5. | ARBITE  | ER VALIDATION                        |    |

| !  | 5.1. E  | MULATING SYSTEMS                     | 55 |

| !  | 5.2. D  | Development Stage Validation         | 56 |

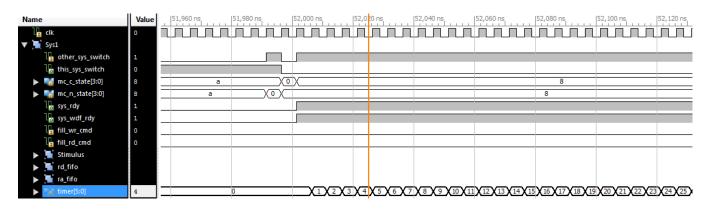

|    | 5.2.1.  | Switching branches                   | 57 |

|    | 5.2.2.  | System-to-Arbiter Write              |    |

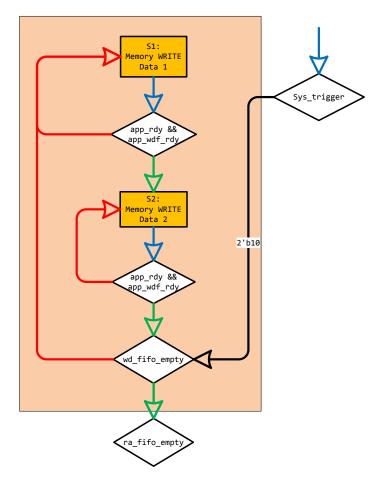

|    | 5.2.3.  | Arbiter executing buffered Writes    | 59 |

|    | 5.2.4.  | Validating all possible cases        | 60 |

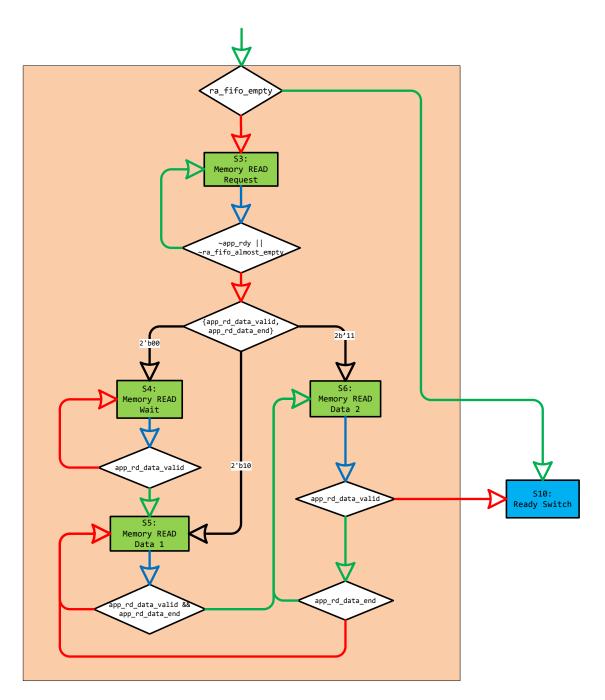

|    | 5.2.5.  | System-to-Arbiter Read commands      | 61 |

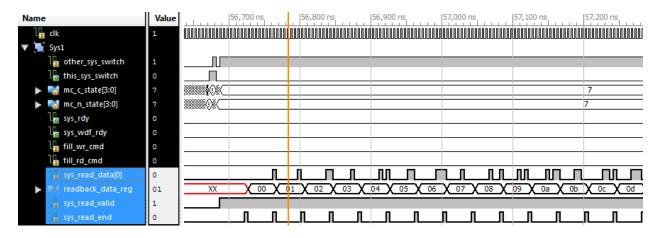

|    | 5.2.6.  | Arbiter-to-System Read execute       | 62 |

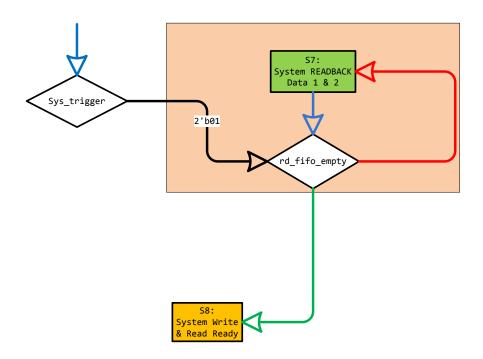

|    | 5.2.7.  | System-to-Arbiter Read-back          | 64 |

| !  | 5.3. F  | UNCTIONALITY CHECKERS                | 65 |

|    | 5.3.1.  | Data as a function of its address    | 65 |

|     | 5.3.2.      | SRAM tracking    | 66 |

|-----|-------------|------------------|----|

| 6.  | CONCLUS     | ON               | 67 |

| APP | ENDIX A: N  |                  | 71 |

| APP | ENDIX B: C  | DDE              | 73 |

| E   | XAMPLE TOP. |                  | 73 |

| U   | SER_DESIGN  | (Arbiter_block)1 | 00 |

| S   | TIMULUS     | 1                | 13 |

| V   | ERILOG TES  | TBENCH1          | 17 |

# **Table of Figures**

| Figure 2.5-1: DRAM Row Access Latency vs. Year [9]17                                          |

|-----------------------------------------------------------------------------------------------|

| Figure 2.5-2: DRAM Column Address Time vs. Year [9]18                                         |

| Figure 3.3-1: Screen Shot of ISE Project Navigator21                                          |

| Figure 3.3-2: Flow Chart and Timing for Simulation and Hardware Validation                    |

| Figure 3.3-3: iSim Screen Shot25                                                              |

| Figure 3.3-4: ChipScope Screen Shot26                                                         |

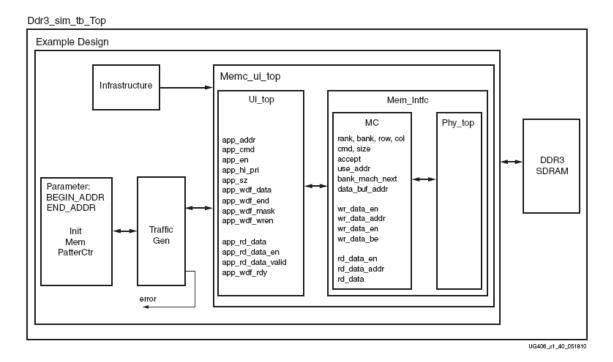

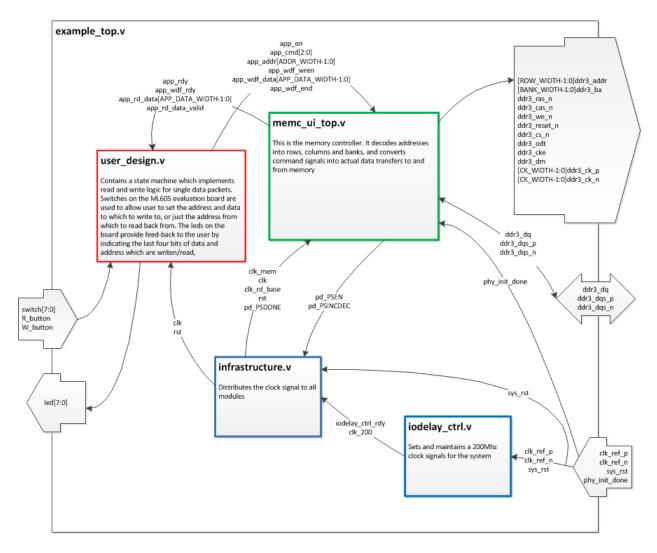

| Figure 4.1-1: Example Design Block Diagram [3]28                                              |

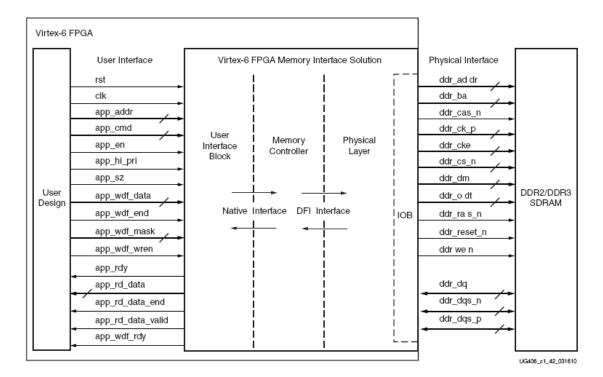

| Figure 4.2-1: User Interface between User Design and Memory [3]                               |

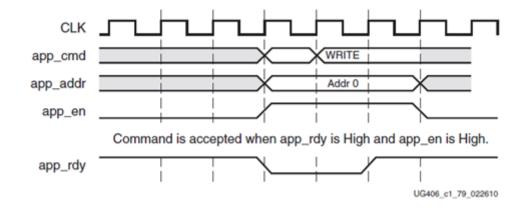

| Figure 4.2-2: Sending a Command and Address to the Memory Controller [3]                      |

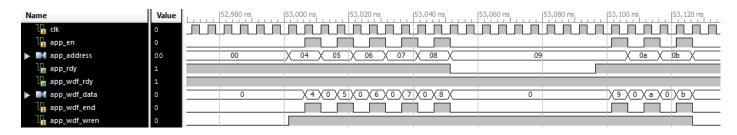

| Figure 4.2-3: Signals Used for Writing [3]33                                                  |

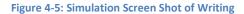

| Figure 4.2-4: Simulation Screen Shot of Writing34                                             |

| Figure 4.2-5: Signal Used for Reading [3]34                                                   |

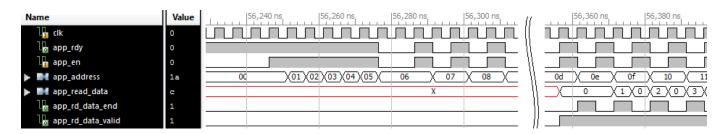

| Figure 4.2-6: Simulation Screen Shot of Reading35                                             |

| Figure 4.3-1: Two arbiter_blocks set-up to connect the DDR3 memory to two different systems41 |

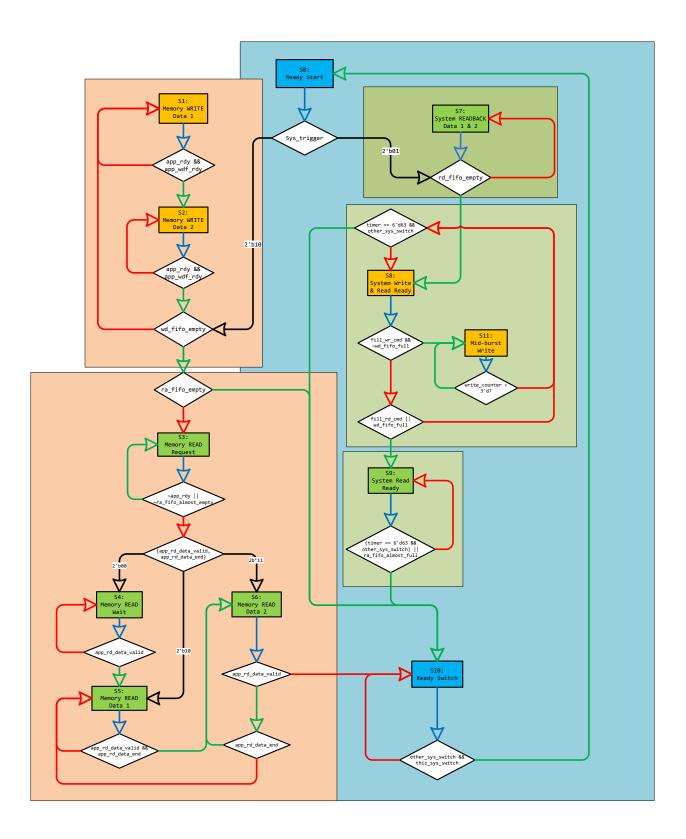

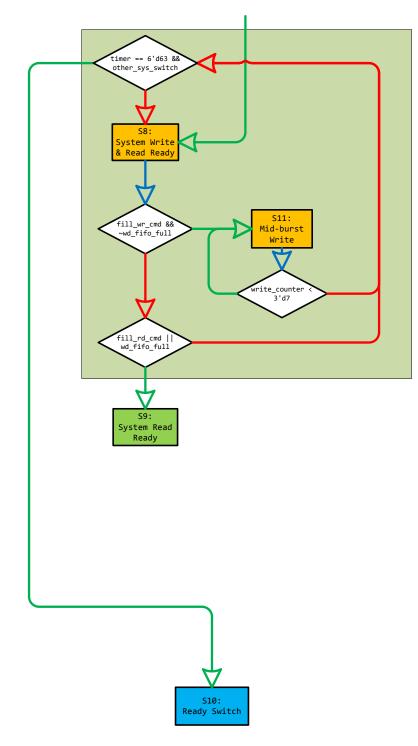

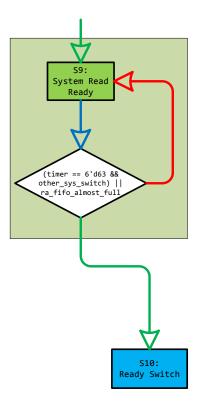

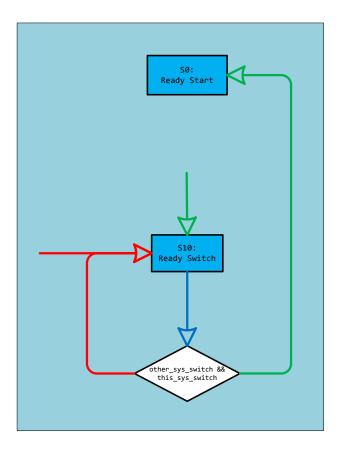

| Figure 4.3-2: Arbiter State Machine Full42                                                    |

| Figure 4.3-3: System-to-Arbiter Write45                                                       |

| Figure 4.3-4: System-to-Arbiter Read46                                                        |

| Figure 4.3-5: Switching Branches47                                                            |

| Figure 4.3-6: Arbiter-to-Memory Write48                                                       |

| Figure 4.3-7: Arbiter-to-Memory Read50                                                        |

| Figure 4.3-8: Arbiter-to-System Read-back51                                                   |

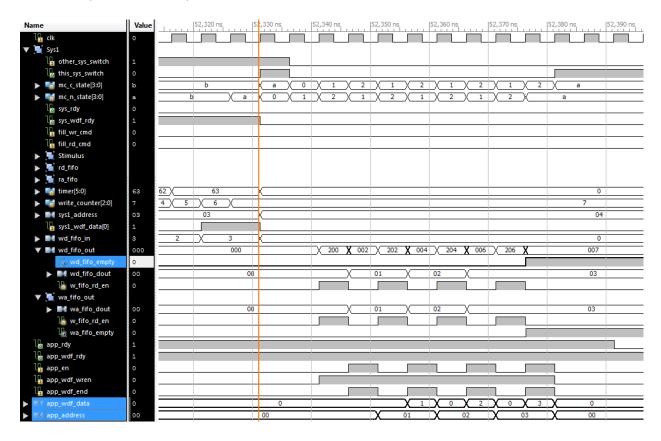

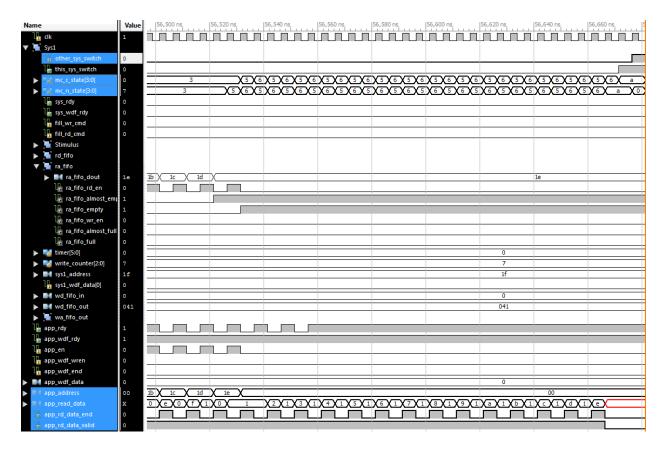

| Figure 5.2-1: Switching Branches57                                                            |

| Figure 5.2-2: System-to-Arbiter Write                                                         |

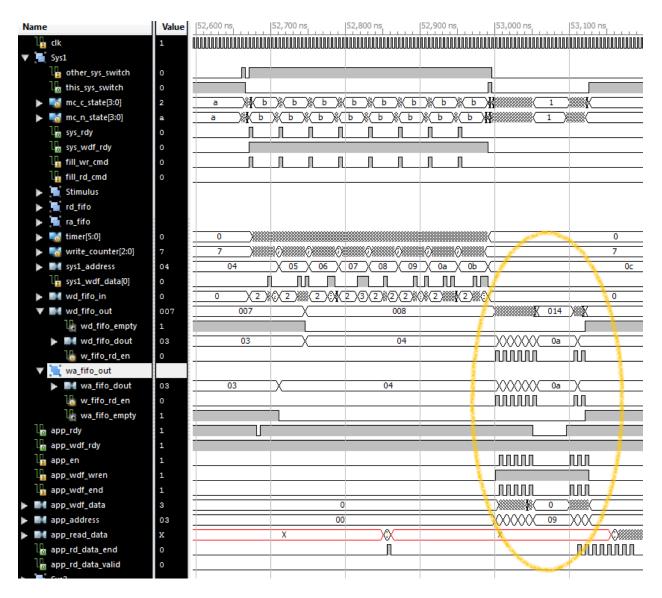

| Figure 5.2-3: Arbiter-to-System Write                  | 59 |

|--------------------------------------------------------|----|

| Figure 5.2-4: Arbiter successfuly avoiding app_rdy low | 60 |

| Figure 5.2-5: System-to-Arbiter read requests          | 61 |

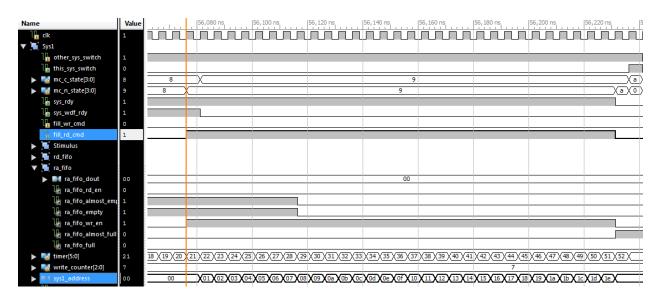

| Figure 5.2-6: Arbiter-to-Memory read execution         | 62 |

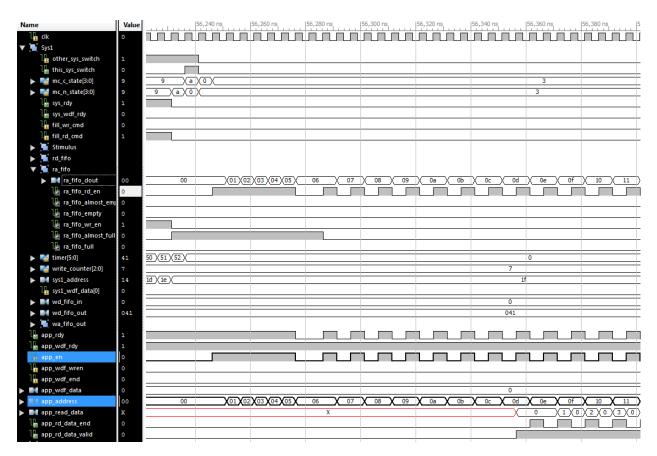

| Figure 5.2-7: Arbiter-to-Memory read-back              | 63 |

| Figure 5.2-8: System-to-Arbiter Read-back              | 64 |

# 1. Introduction

In many applications, it is useful for more than one system to interact with memory. In testing specifically, when the unit under test (UUT) is communicating with memory, there needs to be a second system regulating what the UUT is writing to memory. Teradyne has assigned us the task of developing an arbiter for the latest double data rate memory (DDR3).

Xilinx has released a memory controller for DDR3 which handles everything for communication between one system and memory. If two systems try to read or write to DDR3 memory at the same time, however, there is a great risk the data read or written will not be accurate. The goal of this project is to design a traffic controller, or arbiter, that will delegate which system's turn it is to send requests while blocking requests from the other system. An arbiter will prevent read/write collisions and maintain request order to ensure the memory is holding accurate data.

There are several challenges to designing an arbiter that interacts with a DDR3 memory controller. First is that the arbiter must work around the memory's refresh rate. During a refresh, there can be no communication with the memory. In addition, the arbiter must keep all read and write requests from the systems in order. If one system sends a read before the other sends a write, the read must be executed first. Finally, the arbiter cannot allow one system to use the arbiter for too long. By keeping all these factors in mind, the developed an arbiter should be successful in a testing environment.

The approach to developing the arbiter in this project is to first create a block diagram show how the two systems will interact with memory. Once the block diagram is finished, the task is to develop an arbiter protocol which will keep requests in order and balance access time between the two systems. The first step in implementing the design is to get one system to communicate with the DDR3 memory controller. This involves developing a state machine to fulfill the memory interface protocol specified by the controller. The state machine needs to be able to pause during refresh cycles and pickup where it left off when the refresh cycle is through. The refresh cycle is difficult to detect at the correct time in order to avoid losing or repeating a request. Once one system works completely, the next step is getting two systems to work using the arbiter protocol.

# 2. Background

There are two different types of random access memory: synchronous and dynamic. Synchronous random access memory (SRAM) is used for high-speed, low power applications while dynamic random access memory (DRAM) is used for its low cost and high density. Designers have been working to make DRAM faster and more energy efficient. The following sections will discuss the differences between these two types of RAM, as well as present the progression of DRAM towards a faster, more energy efficient design.

### 2.1. Random Access Memory (RAM)

Today, the most common type of memory used in digital systems is random access memory (RAM). The time it takes to access RAM is not affected by the data's location in memory. RAM is volatile, meaning if power is removed, then the stored data is lost. As a result, RAM cannot be used for permanent storage. However, RAM is used during runtime to quickly store and retrieve data that is being operated on by a computer. In contrast, nonvolatile memory, such as hard disks, can be used for storing data even when not powered on. Unfortunately, it takes much longer for the computer to store and access data from this memory. There are two types of RAM: static and dynamic. In the following sections the differences between the two types and the evolution of DRAM will be discussed. [8]

#### 2.2. Static Random Access Memory (SRAM)

Static random access memory (SRAM) stores data as long as power is being supplied to the chip [8]. Each memory cell of SRAM stores one bit of data using six transistors: a flip flop and two access transistors (i.e. four transistors) [5;9]. SRAM is the faster of the two types of RAM because it does not involve capacitors, which involve sense amplification of a small charge. For this reason, it is used in cache memory of computers .[4] Additionally, SRAM requires a very small amount of power to maintain its data in standby mode [9]. Although SRAM is fast and energy efficient it is also expensive due to the amount of silicon needed for its large cell size [5;10]. This presented the need for a denser memory cell, which brought about DRAM.

# 2.3. Dynamic Random Access Memory (DRAM)

According to Wakerly, "In order to build RAMs with higher density (more bits per chip), chip designers invented memory cells that use as little as one transistor per bit"[8]. Each DRAM cell consists of one transistor and a capacitor [4]. Since capacitors "leak" or lose charge over time, DRAM must have a refresh cycle to prevent data loss [11].

According to a high-performance DRAM study on earlier versions of DRAM, DRAM's refresh cycle is one reason DRAM is slower than SRAM [2]. The cells of DRAM use sense amplifiers to transmit data to the output buffer in the case of a read and transmit data back to the memory cell in the case of a refresh [4]. During a refresh cycle, the sense amplifier reads the degraded value on a capacitor into a D-Latch and writes back the same value to the capacitor so it is charged correctly for 1 or 0 [8]. Since all rows of memory must be refreshed and the sense amplifier must determine the value of a, already small, degenerated capacitance, refresh takes a significant amount of time[4;2]. The refresh cycle typically occurs about every 64 milliseconds [8].The refresh rate of the latest DRAM (DDR3) is about 1 microsecond.

Although refresh increases memory access time, according to a high-performance DRAM study on earlier versions of DRAM, the greatest amount of time is lost during row addressing, more specifically, "[extracting] the required data from the sense amps/row caches" [2]. During addressing, the memory controller first strobes the row address (RAS) onto the address bus. Once the RAS is sent, a sense amplifier (one for each cell in the row) determines if a charge indicating a 1 or 0 is loaded into each capacitor. This step is long because "the sense amplifier has to read a very weak charge" and "the row is formed by the gates of memory cells." [4] The controller then chooses a cell in the row from which to read from by strobing the column address (CAS) onto the address bus. A write requires the enable signal to be asserted at the same time as the CAS, while a read requires the enable signal to be de-asserted. The time it takes the data to move onto the bus after the CAS is called the CAS latency [2].

Although recent generations of DRAM are still slower than SRAM, DRAM is used when a larger amount of memory is required since it is less expensive. For example, in embedded systems, a small block of SRAM is used for the critical data path, and a large block of DRAM is used to satisfy all other needs [6]. The following section will discuss the development of DRAM into a faster, more energy efficient memory.

#### 2.4. Development of DRAM

Many factors are considered in the development of high performance RAM. Ideally, the developer would always like memory to transfer more data and respond in less time; memory would have higher bandwidth and lower latency. However, improving upon one factor often involves sacrificing the other.[2]

Bandwidth is the amount of data transferred per second. It depends on the width of the data bus and the frequency at which data is being transferred. Latency is the time between when the address strobe is sent to memory and when the data is placed on the data bus. DRAM is slower than SRAM because it periodically disables the refresh cycle and because it takes a much longer time to extract data onto the memory bus. Advancements have been, however, to several different aspects of DRAM to increase bandwidth and decrease latency. [2]

Over time, DRAM has evolved to become faster and more energy efficient by decreasing in cell size and increasing in capacity[2]. In the following section, we will look at different types of DRAM and how DDR3 memory has come to be.

#### 2.4.1. DRAM

One of the reasons the original DRAM was very slow is because of extensive addressing overhead. In the original DRAM, an address was required for every 64-bit access to memory. Each access took six clock

14

cycles. For a four 64-bit access to consecutive addresses in memory, the notation for timing was 6-6-6-6. Dashes separate memory accesses and the numbers indicate how long the accesses take. This DRAM timing example took 24 cycles to access the memory four times. [2]

In contrast, more recent DRAM implements burst technology which can send many 64-bit words to consecutive addresses. While the first access still takes six clock cycles due memory accessing, the next three adjacent addresses can be performed in as little as one clock cycle since the addressing does not need to be repeated. During burst mode, the timing would be 6-1-1-1, a total of nine clock cycles.[2] The original DRAM is also slower than its descendants because it is asynchronous. This means there is no memory bus clock to synchronize the input and output signals of the memory chip. The timing specifications are not based on a clock edge, but rather on maximum and minimum timing values (in seconds). [2] The user would need to worry about designing a state machine with idle states, which may be inconsistent when running the memory at different frequencies.

#### 2.4.2. Synchronous DRAM

In order to decrease latency, SDRAM utilizes a memory bus clock to synchronize signals to and from the system and memory. Synchronization ensures that the memory controller does not need to follow strict timing; it simplifies the implemented logic and reduces memory access latency. With a synchronous bus, data is available at each clock cycle. [2]

SDRAM divides memory into two to four banks for concurrent access to different parts of memory. Simultaneous access allows continuous data flow by ensuring there will always be a memory bank read for access [2]. The addition of banks adds another segment to the addressing, resulting in a bank, row, and column address. The memory controller determines if an access addresses the same bank and row as the previous access, so only a column address strobe must be sent. This allows the access to occur much more guickly and can decrease overall latency. [9]

#### 2.4.3. DDR1 SDRAM

DDR1 SDRAM (i.e. first generation of SDRAM) doubles the data rate (hence the term DDR) of SDRAM without changing clock speed or frequency. DDR transfers data on both the rising and falling edge of the clock, has a pre-fetch buffer and low voltage signaling, which makes it more energy efficient than previous designs.[2]

Unlike SDRAM, which transfers 1 bit per clock cycle from the memory array to the data queue, DDR1 transfers 2 bits to the queue in two separate pipelines. The bits are released in order on the same output line. This is called a 2n-prefetch architecture. In addition, DDR1 utilizes double transition clocking by triggering on both the rising and falling edge of the clock to transfer data. As a result, the bandwidth of DDR1 is doubled without an increase in the clock frequency. [2]

In addition to doubling the bandwidth, DDR1 made advances is energy efficiency. DDR1 can operate at 2.5 V instead of the 3.3V operating point of SDRAM thanks to low voltage signaling technology.[2]

#### 2.4.4. DDR2 SDRAM

Data rates of DDR2 SDRAM are up to eight times more than original SDRAM. At an operation voltage of 1.8V, it achieves lower power consumption than DDR1. DDR2 SDRAM has a 4-bit prefetch buffer, an improvement from the DDR1 2-bit prefetch. This means that 4 bits are transferred per clock cycle from the memory array to the data bus, which increases bandwidth. [2]

#### 2.4.5. DDR3 SDRAM

DDR3 provides two burst modes for both reading and writing: burst chop (BC4) and burst length eight (BL8)[3]. BC4 allows bursts of four by treating data as though half of it is masked. This creates smooth transitioning if switching from DDR2 to DDR3 memory. [1] However, burst mode BL8 is the primary burst mode. BL8 allows the most data to be transferred in the least amount of time; it transfers the greatest number of 64-bit data packets (eight) to or from consecutive addresses in memory, which means

addressing occurs once for every eight data packets sent. In order to support a burst length of eight data packets, DDR3 SDRAM has an 8-bit prefetch buffer.

DDR3, like its predecessors, not only improves upon bandwidth, but also energy conservation. Power consumption of DDR3 can be up to 30 percent less than DDR2. The DDR3 operating voltage is the lowest yet, at 1.5 V, and low voltage versions are supported at voltages of 1.35 V.

#### 2.5. Timeline

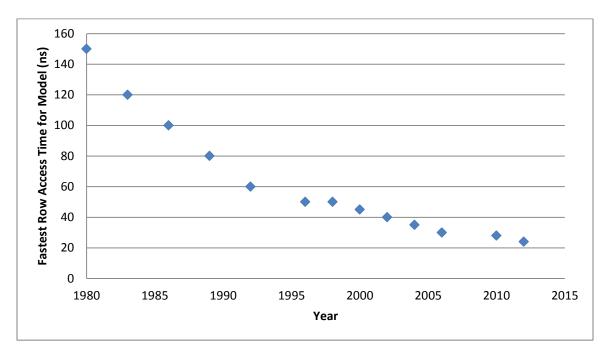

Ideally, memory performance would improve at the same rate as central processing unit (CPU) performance. However, memory latency has only improved about five percent each year [9]. The longest latency (RAS latency) of the newest release of DRAM for each year is shown in the plot in Figure

As seen in Figure 2.5-1, the row access latency decreases linearly with every new release of DRAM until 1996. Once SDRAM is released in 1996, the difference in latency from year to year is much smaller. With recent memory releases it is much more difficult to reduce RAS latency. This can be seen

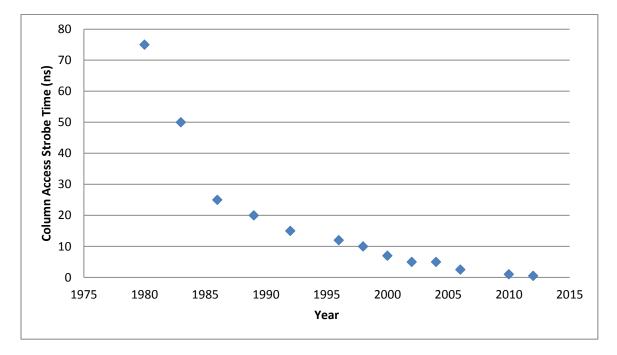

especially for DDR2 and DDR3 memory releases 2006 to 2012. CAS latency, unlike RAS latency, consistently decreases (bandwidth increases) with every memory release, and in the new DDR3 memory, is very close to 0 ns. Figure 2.5-2 shows the column access latency.

Figure 2-2: DRAM Column Address Time vs. Year [9]

Looking at some prominent areas of the CAS graph, it can be seen in Figure 2.5-2 that bandwidth greatly increased (CAS decreased) from 1983 to 1986. This is due to the switch from NMOS DRAMs to CMOS DRAMs [9]. In 1996 the first SDRAM was released. The CAS latency decreased (bandwidth increased) due to synchronization and banking. In later years, the CAS latency does not decrease by much, but this is expected since the latency is already much smaller.

Comparing Figure 2.5-2 to Figure 2.5-1, CAS time decreases much more drastically than RAS time. This means the bandwidth greatly improves, while latency improves much more slowly. In 2010, when DDR2 was released, it can be seen that latency was sacrificed (Figure 2.5-1) for an increase in bandwidth (Figure 2.5-2). [9]

# 3. Methodology

In this section the ML605 and Virtex-6 board hardware is described as well as the tools utilized for design and validation. The Xilinx Integrated Software Environment (ISE) was used for design and iSim and ChipScope were used for validation in simulation and in hardware.

#### 3.1. Hardware

#### 3.1.1. Virtex-6 FPGA

The Virtex-6 FPGA (XC6VLX240T) is used to implement the arbiter. This FPGA has 241, 152 logic cells and is organized into banks (40 pins per bank) [15;14]. These logic cells, or slices, are composed of four lookup tables (LUTs), multiplexers, and arithmetic carry logic. LUTs implement boolean functions, and multiplexers enable combinatorial logic. Two slices form a configurable logic block (CLB). [16].

In order to distribute a clock signal to all these logic blocks, the FPGA has five types of clock lines: BUFG, BUFR, BUFIO, BUFH, and high-performance clock. These lines satisfy "requirements of high fanout, short propagation delay, and extremely low skew"[15]. The clock lines are also split into categories depending on the sections of the FPGA and components they drive. The three categories are: global, regional, and I/O lines. Global clock lines drive all flip-flops, clock enables, and many logic inputs. Regional clock lines drive all clock destinations in their region and two bordering regions. There are six to eighteen regions in an FPGA. Finally, I/O clock lines are very fast and only drive I/O logic and serializer/deserializer circuits. [15]

#### 3.1.2. ML605 Board

The Virtex-6 FPGA is included on the ML605 Development Board. In addition to the FPGA, the development board includes a 512 MB DDR3 small outline dual inline memory module (SODIMM), which our design arbitrates access to. A SODIMM is the type of board the memory is manufactured on [9]. The FPGA also includes 32 MB of linear BPI Flash and 8 Kb of IIC EEPROM.

Communication mechanisms provided on the board include Ethernet, SFP transceiver connector, GTX port, USB to UART bridge, USB host and peripheral port, and PCI Express. [13] The only connection used during this project was the USB JTAG connector. It was used to program and debug the FPGA from the host computer.

There are three clock sources on the board: a 200 MHz differential oscillator, 66 MHz singleended oscillator and SMA connectors for an external clock.[13] This project utilizes the 200MHz oscillator.

Peripherals on the ML605 board were useful for debugging purposes. The push buttons were used to trigger sections of code execution in ChipScope such as reading and writing from memory. Dip switches acted as configuration inputs to our code. For example, they acted as a safety to ensure the buttons on the board were not automatically set to active when the code was downloaded to the board. In addition, the value on the switches indicated which system would begin writing first for debugging purposes. LEDs were used to check functionality of sections of code as well, and for additional validation, they can be used to indicate if an error as occurred. Although we did not use it, the ML605 board provides an LCD.

#### **3.2. Tools**

Now that the hardware where the design is placed is described, the software used to manipulate the design can be described. The tools for design include those provided within Xilinx Integrated Software Environment, and the tools used for validation include iSim and ChipScope. This looks at the turn-around time for both validation tools and what it means for the design process.

#### **3.2.1. Xilinx Integrated Software Environment (ISE)**

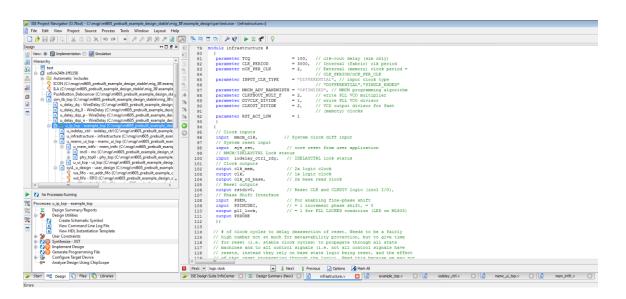

We designed the arbiter using Verilog hardware description language in Xilinx Integrated Software Environment (ISE). ISE is an environment in which the user can "take [their] design from design entry through Xilinx device programming"[14]. The main workbench for ISE is ISE Project Navigator. The Project Navigator tool allows the user to effectively manage their design and call upon development processes. In Figure 3.3-1, a screen shot of ISE Project Navigator can be seen.

Figure 3-1: Screen Shot of ISE Project Navigator

Figure 3.3-1 shows some main windows in ISE Project Navigator. On the right hand side is the window for code entry. The hierarchal view of modules in the design appears on the left, and when implementation is selected from the top, the design implementation progress is shown in the bottom window. If simulation were selected instead of implementation there would be an option to run the design for simulation.

The main processes called upon by ISE are synthesis, implementation, and bit stream generation. During synthesis, Xilinx Synthesis Technology (XST) is called upon. XST synthesizes Verilog, VHDL or mixed language designs and creates netlist files. Netlist files, or NGC files, contain the design logic and constraints. They are saved for use in the implementation process. During synthesis, the XST checks for synthesis errors (parsing) and infers macros from the code. When the XST infers macros it recognizes parts of the code that can be replaced with components in its library such as MUXes, RAMs, adder and subtracters. In addition to inferring macros, the XST recognizes finite state machines and encodes them in a way that would be best for reduced area and/or increased speed. [14]

Implementation is the longest process to perform on the design. The first step of implementation is to combine the netlists and constraints into a design/NGD file. The NGD file is the design file reduced to Xilinx primitives. This process is called translation. During the second step, mapping, the design is fitted into the target device. This involves turning logic into FPGA elements such as configurable logic blocks. Mapping produces a native circuit description (NCD) file. The third step, place and route, uses the mapped NCD file to place the design and route timing constraints. Finally, the program file is generated and, at the finish of this step, a bitstream is ready to be downloaded to the board. [14]

#### 3.2.2. Synthesis and Simulation

Once the design has been synthesized, simulation of the design is possible. Simulating a design enables verification of logic functionality and timing [14]. We used simulation tool in ISE (isim) to view timing and signal values. In order to utilize isim, we created a test bench to provide the design with stimulus. Since simulation only requires design synthesis, it is a relatively fast process. The short turn-around time of simulation means we were able to iteratively test small changes to the design and, therefore, debug our code efficiently.

#### 3.2.3. Implementation and Hardware Validation

Once the design was working in simulation, we still needed to test the design's functionality in hardware. Testing the design in hardware is the most reliable validation method. In order to download the design to the board, it first needs to be implemented in ISE. Implementation has a much longer turnaround time than synthesis, so while functionality in hardware ensures the design is working, simulation is the practical choice for iterative verification. In order to test our design in hardware, we utilized ChipScope Pro Analyzer, a GUI which allows the user to "configure [their] device, choose triggers, setup the console, and view results of the capture on the fly" [12]. In order to use ChipsScope Pro, you may either insert ChipScope Pro Cores into the design using the Core Generator, a tool that can be accessed in ISE Project Navigator, or utilize the PlanAhead or Core Inserter tool, which automatically inserts cores into the design netlist for you. [12]

One method of inserting ChipScope cores into the design is by utilizing PlanAhead software. The PlanAhead tool enables the creation of floorplans. Floorplans provide an initial view of "the design's interconnect flow and logic module sizes" [17,59]. This helps the designer to "avoid timing, utilization, and routing congestion issues" [17, 112]. PlanAhead also allows the designer to create and configure I/O ports and analyze implementation results, which aids in the discovery of bottlenecks in the design[17]. For our project, however, we utilized PlanAhead only for its ability to automatically insert ChipScope cores. PlanAhead proved to be inefficient for our purposes since many times, when a change was made in the design, the whole netlist would need to be selected again. In addition, there were bugs in the software that greatly affected the turn-around time of debugging, and it crashed several times. If PlanAhead were used for floor planning and other design tools, then it might have proved to be much for useful.

In replace of PlanAhead, we utilized the Core Generator within ISE. The ChipScope cores provided by Xilinx include ICON, ILA, VIO, ATC2, and IBERT. The designer can choose which cores to insert by using the Core Generator in ISE. The ICON core provides communication between the different cores and the computer running ChipScope. [14] It can connect up to fifteen ILA, VIO, and ATC2 cores [12]. The ILA core is used to synchronously monitor internal signals. It contains logic to trigger inputs and outputs and capture data. ILA cores allow up to sixteen trigger ports, which can be 1 to 256 bits wide. The VIO core can monitor signals like ILA, but also drive internal FPGA signals real-time. The ATC2 core is similar to the ILA core, but was created for Agilent FPGA dynamic probe technology. Finally, the IBERT

23

core contains "all the logic to control, monitor, and change transceiver parameters and perform bit error ratio tests" [12,19].

The only ChipScope cores we were concerned with in this project were the ICON and ILA cores. We inserted one ChipScope ILA and ICON cores using the ISE Core Generator within ISE Project Navigator. The ILA core allowed us to monitor internal signals in the FPGA. Instead of inserting a VIO core, which allows inputs to and outputs from ChipScope, we used buttons to trigger the execution of write and read logic.

#### 3.2.4. Analysis of Turn-Around Times

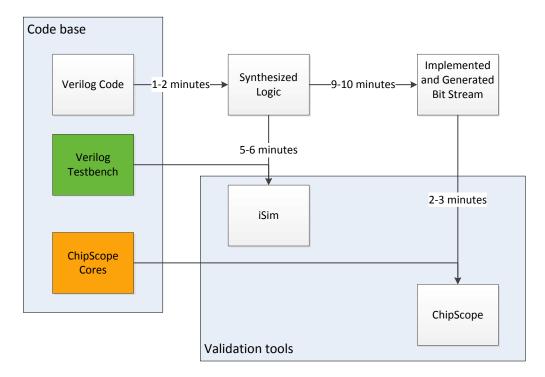

As introduced in sections 3.3.2 and 3.3.3, implementation takes much longer than synthesis. Therefore, when it comes down to turn-around time, simulation is much more effective for iterative debugging. In Figure 3.3-2, the phases for simulation and hardware validation can be seen as well as the time it takes to complete each phase.

Figure 3-2: Flow Chart and Timing for Simulation and Hardware Validation

For simulation, the process starts at Verilog code, becomes synthesized logic, and using a testbench, is run in iSim for viewing. This process takes about eight minutes total. A system's simulation run-time is much longer than if it were running on hardware, but simulation is still faster than hardware validation because it does not have to undergo implementation. The bottleneck in our simulation process is the set up time for the DDR3 memory model which accounts for most of the simulation time.

Hardware validation starts at Verilog code, is synthesized, implemented, and imported into ChipScope. This whole process takes about fifteen minutes. Most of the time spent for hardware validation is on implementation of the design. In addition, hardware validation requires more of the user's attention. It is more difficult and takes more time to set up a ChipScope core than it does to create a test bench for simulation. While a test bench (green) involves writing some simple code, a ChipScope core (orange) involves setting up all the signals to be probed. Not only is simulation faster, but the iSim tool is easier to use than ChipScope. Figure 3.3-3 shows a screen shot of iSim.

| ISim (0.76xd) - [template_02_15<br>File Edit View Simulation |             | rout Help                    |                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |             |                   |                   |                   |                                         |                   |                   |             |

|--------------------------------------------------------------|-------------|------------------------------|---------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|-------------------|-------------|

|                                                              |             |                              | K                   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |             |                   |                   |                   |                                         |                   |                   |             |

| 🗋 ờ 🔚 👹 🛛 🖓 🗋 🔞                                              | X 🕲 🛛 🖓 X   | AA 😹 🗍 î 😳                   | 8809 /              | ' K?   🎤 🎤 🤉   | ) 🍠 🖻 🗠 🗠 🕇 🔊 🐴                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 🔄 🕨 🖟 1.00us 💌                          | 5a      🖵 E | te-launch         |                   |                   |                                         |                   |                   |             |

| tances and Processes                                         | ⇔⊡∂×        | Objects                      |                     | ⇔⊡∂×           | <b>₽</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |             |                   |                   |                   |                                         |                   |                   |             |

|                                                              |             | Simulation Objects for s     | im_tb_top           |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |             |                   |                   |                   |                                         |                   |                   |             |

|                                                              |             | THEFT                        | IB 😫                |                | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Value                                   |             | 17,685,154,300 fs | 17,685,154,400 fs | 17,685,154,500 fs | 17,685,154,600 fs                       | 17,685,154,700 fs | 17,685,154,800 fs | 17,685,154, |

| stance and Process Name                                      | Design Unit |                              |                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                       |             |                   |                   |                   |                                         |                   |                   |             |

| sim_tb_top                                                   | sim_tb_top  | Object Name                  | Value               | Data Type 🔶    | L app_rdy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                       |             |                   |                   |                   |                                         |                   |                   |             |

| 🧧 gibi                                                       | gibi        | l sys_clk_p                  | 1                   | Logic          | (3) 1 app_en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                       |             |                   |                   |                   |                                         |                   |                   |             |

|                                                              |             | le sys_clk_n                 | 0                   | Logic          | App_address     App_ad | 00                                      |             |                   |                   |                   | 00                                      |                   |                   | _           |

|                                                              |             | l@ clk_ref_p                 | 1                   | Logic          | 1 app_read_data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | x                                       |             |                   |                   |                   | X                                       |                   |                   | _           |

|                                                              |             | l@ clk_ref_n                 | 0                   | Logic          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |             |                   |                   |                   | ×                                       |                   |                   | _           |

|                                                              |             | ddr3_parity                  | 1                   | Logic          | →r app_rd_data_end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                       |             |                   |                   |                   |                                         |                   |                   |             |

|                                                              |             | ddr3_reset_n                 |                     | Logic =        | app_rd_data_valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                       |             |                   |                   |                   |                                         |                   |                   |             |

|                                                              |             |                              | . 22222222222222222 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                       |             |                   |                   |                   | 0                                       |                   |                   |             |

|                                                              |             |                              |                     | Array          | app_wdf_data[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                       |             |                   |                   |                   |                                         |                   |                   |             |